# Low Leakage Approximate multiplier design for high Performance Error Tolerant Applications

# Supratim Saha<sup>1</sup>, Dr. Amit Kumar Jain<sup>2</sup>

<sup>1,2</sup> Department of Electronics & Communication Engineering Shri Venkateshwara University, Gajraula, Uttar Pradesh, India <sup>1</sup>supratimsaha2009@gmail.com, <sup>2</sup>rinku.j19@gmail.com

#### ABSTRACT

Power dissipation has become a major concern in VLSI circuit design with the rapid launch of battery powered applications. In highperformance constructions, the leakage component of power consumption is comparable to the switching component. This percentage increases as the technology scales unless effective leak control techniques are in place. In the case of fault-tolerant applications it is also not necessary to adhere to the exact calculation method. Therefore, an approximate multiplier of 8 x 8 is developed in this article using several proposed techniques to reduce leakage power such as MTCMOS, DUAL-Vt, and LECTOR. All of the above techniques are simulated with a tanning tool using 90 nm technology.

#### Keywords

High-performance constructions , Leakage current, power dissipation, Dynamic power, MTCMOS, Dual-Vt, LECTOR

Article Received: 10 August 2020, Revised: 25 October 2020, Accepted: 18 November 2020

## Introduction

Approximate Computing (AC) is a wide range of techniques that reduce the precision of a computation to improve performance, power, and / or other quality metrics. AC takes advantage of the fact that some critical applications like machine learning and media processing do not require accurate results to be useful. For example, we can use a lower resolution image encoder in applications that do not require high quality images.

## **Technology Scaling**

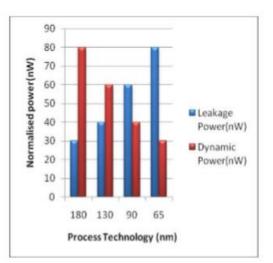

Power dissipation is an important consideration in VLSI CMOS circuit design. High power consumption leads to reduced battery life in battery-powered applications and affects reliability, packaging and cooling costs. The main sources of power dissipation are: 1) capacitive power dissipation due to the charging and discharging of the load capacitor; 2) short-circuit currents due to the presence of a conductive path between the supply voltage and earth for the short time during the transition of the halogen; and 3) the leakage current. The leakage current consists of reverse bias diode currents and currents below the threshold. The first is due to the charge stored between the drain and the bulk of the active transistors, while the second is due to carrier diffusion between the source and drain of the OFF transistors.

Fig. 1. Leakage and Dynamic power consumption with technology scaling

## **Approach To Analyse**

The market demand and efficient portable electronic equipment have pushed the industry to produce circuit designs operating at low voltage (LV) for low power (LP) consumption. Reducing the supply voltage reduces the dynamic power quadratic ally and leakage power linearly to the first order. Hence, supply voltage scaling has remained the major focus of the low power design. This has resulted in circuits operating at a supply voltage lower than the threshold voltage of a transistor (i.e. subthreshold region). One of the main contributors for the static power consumption is sub-threshold leakage current, the drain to source current when the gate voltage is smaller than the threshold voltage. As the technology feature size shrink sub threshold leakage current increases exponentially due to the decrease of threshold voltage. According to the International Technology Roadmap for Semiconductors (ITRS) [1]. However, reduction in supply voltages requires

that threshold voltage (VT) also be scaled down proportionally. Devices with lowered VT would dissipate more leakage power in standby mode, dominated by subthreshold leakage current. This can be very significant in burst-mode type electronic circuits. Three main components of leakage mechanisms in scaled devices can be readily identified as Gate leakage, sub-threshold leakage and Band-To-Band Tunnelling (BTBT) leakage [2].

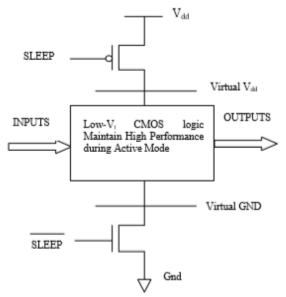

Fig 2: General MTCMOS circuit architecture

Multi-threshold CMOS (MTCMOS) is a design technique in which high threshold sleep transistors are connected between the logic circuit and power or ground, thus creating a virtual supply rail or virtual ground rail, respectively. The low threshold voltage transistors which have high performance are used to reduce the propagation delay time in the critical path. The high-threshold voltage transistors which have less power consumption are used to reduce the power consumption in the shortest path [4],[5]. There are methods high threshold voltage (HTV) is assigned to transistors of some gates in the non-critical paths while specifying the low-threshold voltage for the gates in the critical path. In this technique, no additional transistors are required as in the case of multithreshold voltage technique. Reduction of static power is achieved while maintaining the same performance as single threshold voltage circuit [6], [7].

#### **Existing Method**

One of the main contributors for the static power consumption is sub-threshold leakage current, the drain to source current when the gate voltage is smaller than the threshold voltage. As the technology feature size shrink subthreshold leakage current increases exponentially due to the decrease of threshold voltage. According to the International Technology Roadmap for Semiconductors (ITRS) [1], leakage power dissipation may eventually dominate total power consumption as technology feature sizes shrink to nanometer regime in deep submicron technologies. The method existing right now consists of various methods & techniques which are used for reducing the leakage power in VLSI circuits.

The low-power and high performance design requirements of modern VLSI technology can be achieved by using MTCMOS technology. Low, normal and high threshold voltage transistors are used to design a CMOS circuit in this technique. With the scaling of CMOS technology, Supply and threshold voltages are reduced. Sub threshold leakage current increases exponentially with lowering of threshold voltage.

#### **Proposed Method**

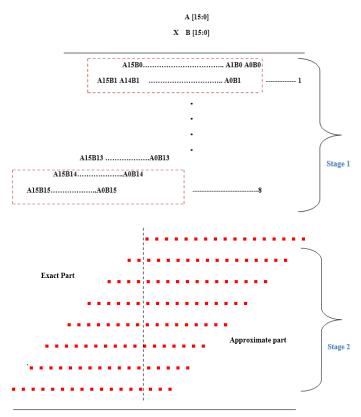

The memory in various components is designed to process at high performance speed. These memory devices also having the challenge to reduce the delay to the decoder as it will improve the overall processing of the system. CMOS is one such device that requires reducing the delay. The optimization of a VLSI design can be done by reducing the transition of information to the decoder.[8]The proposed approach involves two main steps. In the first case, the lossy compression is done through logical clustering. These steps and the variable compression method are described below. Logical Compression: The design of parallel multiplication is usually divided into three successive stages: Adders for Partial Product Formation, Accumulation and Transport Propagation In a multiplier (N  $\times$  N), N2 AND gates are used in parallel to generate the partial product bit matrix. This matrix is then accumulated per column to produce the final product using carry propagation adders. The proposed approach starts with the generation of all partial products using the same number of AND gates, similar to conventional multiplication. Before proceeding with the accumulation step, the number of bits in the partial product matrix is reduced by performing a lossy logic compression. The aim is to reduce the number of rows in the partial product matrix and thus obtain material with low complexity before proceeding with the accumulation. Commutative reassignment: The logical compression step reduces the number of sub-terms of the product. This reduction can be used to reduce the number of lines before the accumulation step. This can be achieved by reallocating the terms of the partial product based on the commutative property of the bits; H. Bits of the same weight are collected in the same column. A partial product is generated using an AND gate, and the outputs generated by the gate are then approximated using an array of half OR gates. A reduced set of preprocessed partial product matrix can thus be accumulated by applying any practical multiplication scheme such as the save-carry table, Wallace and the dadda tree. In theory, an OR gate with two inputs is sufficient to sum two bits, i.e. '0' + 1' = 1' + 0' = 1' 0' OR' = 1' OR 0' = 1' and also' + 0' = 0''=' 0'OR'0 '=' 0 '. However, the OR gate does not provide an exact sum when both inputs are high, i.e. H. "1" + "1" = "1"OR "1", the adder returns "10" and the OR outputs "

Final sum Fig 3 : Proposed approximation Algorithm

For the proposed approximate multiplier, the techniques that are applied in the existing multiplier are applied to reduce the static power consumption, which is the dominant in lower technologies. Hence along with approximation, we are also implementing the Leakage power techniques such as Modified MTCMOS, DUAL-VT and LECTOR techniques that are used in the existing multiplier to reduce the leakage power which is result of drastic scaling.

Results

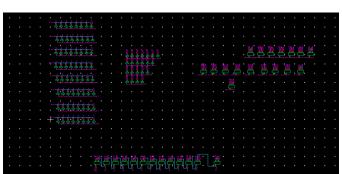

Fig. 4 : Schematic diagram of 8X8 Proposed approximate multiplier using MTCMOS technique

Fig. 5: Waveform of 8X8 Proposed approximate multiplier using MTCMOS technique

Fig. 6: Schematic diagram of 8X8 Proposed approximate multiplier using Dual Vt technique

Fig. 7: Waveform of 8X8 Proposed approximate multiplier using Dual Vt technique

Fig. 8 Schematic diagram of 8X8 Proposed approximate multiplier using Lector technique

Fig. 9: Waveform of 8X8 Proposed approximate multiplier using Lector technique

| Name of technique                          | Area(transistor count) | Delay(ns) | Power(mw) |

|--------------------------------------------|------------------------|-----------|-----------|

| Existing<br>multiplier<br>using Dual<br>Vt | 2008                   | 1.21      | 44.8      |

| Existing<br>multiplier<br>using<br>Lector  | 2120                   | 2.02      | 200       |

| Existing<br>multiplier<br>using<br>MTCMOS  | 2120                   | 1.32      | 55        |

| Proposed<br>multiplier<br>using Dual<br>Vt | 1386                   | 1.04      | 29        |

| Proposed<br>multiplier<br>using<br>Lector  | 1446                   | 1.16      | 117       |

| Proposed<br>multiplier<br>using<br>MTCMOS  | 1446                   | 1.12      | 33.2      |

Fig.10 Comparison between existing and proposed multiplier

## Conclusions

In this paper, an approximate 8x8 approximate multiplier is designed with different leakage power reduction techniques like Multi-Vt, Dual-Vt, LECTOR to improve the performance in terms of delay, area and power. Simulation results in tanner tool show that the proposed method shows better results in terms of power, area and delay reports when compared to existing multiplier.

## References

- J. Han and M. Orshansky, "Approximate computing: An emerging paradigm for energy-efficient design," 2013 18th IEEE European Test Symposium (ETS), Avignon, 2013, pp. 1-6.

- [2] Q. Xu, T. Mytkowicz and N. S. Kim, "Approximate Computing: A Survey," in IEEE Design & Test, vol. 33, no. 1, pp. 8-22, Feb. 2016.

- [3] James T. Kao and Anantha P. Chandrakasan, "DualThreshold Voltage Techniques for Low-Power Digital Circuits," IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 35, NO. 7, JULY 2000.

- [4] ShyamAkashe, Nitesh Kumar Tiwari, JayramShrivas and Rajeev Sharma, "A Novel High Speed & Power Efficient Half Adder Design Using MTCMOS Technique in 45 Nanometre Regime" IEEE International Conference on Advanced Communication Control and Computing Technologies (ICACCCT) 2012.

- [5] MilindGautam and ShyamAkashe, "Reduction of Leakage Current and Power in Full Subtractor Using MTCMOS Technique" 2013 International Conference on Computer Communication and Informatics (ICCCI 2013), Jan. 04 – 06, 2013.

- [6] J. Jaffari and A. Afzali-Kusha, "New Dual-Threshold Voltage Assignment Technique for Low-Power Digital Circuits," 0-7803-8656-6/04/\$20.00, pp.413-416 IEEE 2004.

- [7] L. Wei. 2. Chen, K. Roy, M. C. Johnson, Y. Ye and V. De, "Design and optimization of dual threshold circuits for

low voltage low power applications," IEEE Transactions on VLSI Systems. Vol. 7. No. 1, pp. 16-24. Mar. 1999.

- [8] Supratim Saha1, Dr. Amit Kumar Jain2 "Analysis of Control Strategies of Leakage Power Considering Decoder Optimization" Solid State Technology ISSN 0038-111X, Vol-63 Issue-5, 2021.

- [9] International Technology Roadmap for Semiconductors by Semiconductor Industry Association, 2002. [Online] Available http://public.itrs.net

- [10] H. Soeleman et al, Proc. of ISLPED, pp. 94-96, 1998

- [11] K.Roy and S.C.Prasad, "Low-power CMOS VLSI ciruit design". New York: Wiley, 2000, ch.5, pp.214-219

- [12] Y. Tsividis and C.McAndrew, Operation and Modeling of the MOS Transistor, 3rd Ed.Oxford University Press, 2011.

- [13] Abhinov, SanjeevRai and Rajeev Tripathi: A robust Design for Ultra Low Power Operation using Dynamic Threshold SCL Logic, Int. Conf. on Comp. and Commun. Tech (ICCCT)-2011.

- [14] A. Wang, B.H. Calhoun, A.P. Chandrakasan, Sub-threshold Design for Ultra Low-power Systems, Springer, 2006.

- [15] BrankoDokic and AleksandarPajkanovic, Low Power CMOS Subthreshold Circuits ,MIPRO 2013, May 20-24, 2013, Opatija, Croatia

- [16] S. Kang and Y.Leblebici, CMOS Digital Integrated Circuits, McGrawHill, New York, 2003.

- [17] M.GeethaPriya, Dr.K.Baskaran. D.Krishnaveni, Leakage Power Reduction Techniques in Deep Submicron Applications, Technologies for VLSI International Conference on Communication Technology and System Design 2011

- [18] Wei, L., Chen, Z., Johnson, M., Roy, K. and De, V., "Design and Optimization of Low Voltage High Performance Dual Threshold CMOS Circuits", Proceedings

of the 35th Design Automation Conference (DAC), 1998, pp. 489-494.

- [19] Mutoh, S., Douseki, T., Matsuya, Y., Aoki, T., Shigematsu, S., and Yamada, J., "1-V Power Supply High-Speed Digital Circuit Technology with Multithreshold-Voltage CMOS," IEEE Journal of Solid-State Circuits 30, August 1995, pp. 847-854.

- [20] Kawaguchi, H., Nose, K., and Sakurai, T. " A Super Cut-Off CMOS (SCCMOS) Scheme for 0.5-V Supply Voltage with Pico ampere Stand-By Current," IEEE Journal of Solid State Circuits vol.35,n.10, October 2000, pp.1498-1501.

- [21] Kao, J. T., and Chandrakasan, A. P. "Dual-Threshold Voltage Techniques for Lowpower Digital Circuits," IEEE Journal of Solid State Circuits, vol.35, no.7, July 2000, pp.1009-1018.